# 8051 Embedded CRT Monitor Controller MASK Version

# FEATURES

- 8051 core.

- 384-bytes internal RAM.

- 16K-bytes program Mask ROM.

- 14-channels 10V open-drain PWM DAC, 10 dedicated channels and 4 channels shared with I/O pin.

- 28 bi-direction I/O pin,12 dedicated pin,12 shared with DAC,4 shared with DDC/IIC interface.

- 5-output pin shared with H/V sync output and self test output pins.

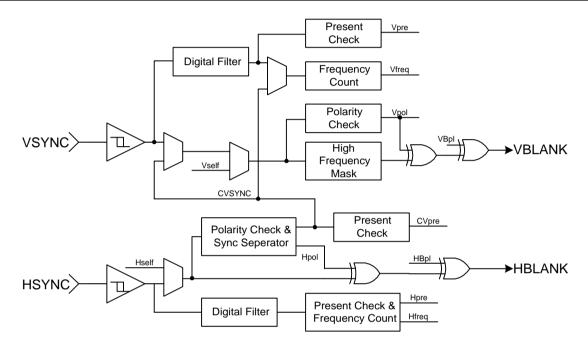

- SYNC processor for composite separation, polarity and frequency check, and polarity adjustment.

- Built-in monitor self-test pattern generator.

- Built-in low power reset circuit.

- One slave mode IIC interface and one master mode IIC interface.

- IIC interface for DDC1/DDC2B and EEPROM; only one EEPROM needed to store DDC1/DDC2B and display mode information.

- Dual 4-bit ADC or 4 channel 6-bit ADC.

- Watchdog timer with programmable interval.

- 40-pin PDIP and 44-pin PLCC package.

# **GENERAL DESCRIPTION**

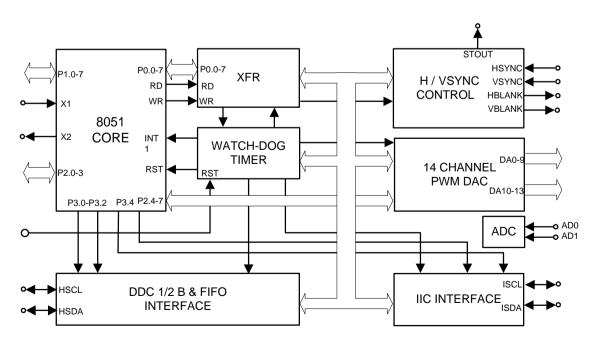

The MTV112A micro-controller is an 8051 CPU core embedded device specially tailored to CRT monitor applications. It includes an 8051 CPU core, 384-byte SRAM, 14 built-in PWM DACs, DDC1/DDC2B interface, 24Cxx series EEPROM interface, A/D converter and a 16K-bytes internal program Mask ROM.

# BLOCK DIAGRAM

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

MYSON TECHNOLOGY

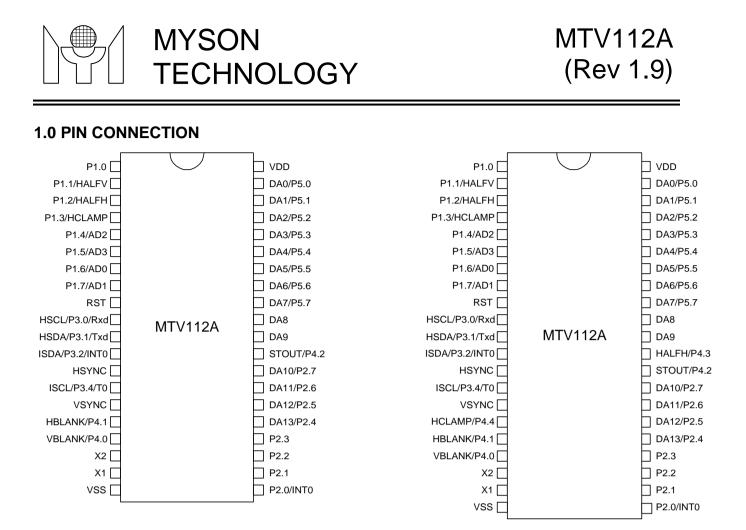

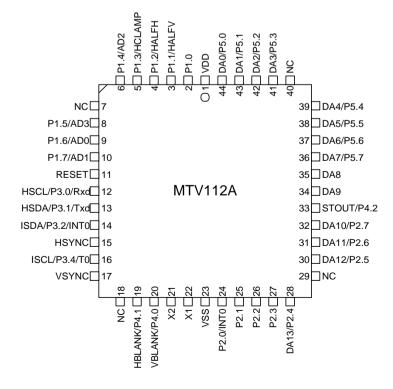

# **2.0 PIN DESCRIPTIONS**

| Name           | <b>T</b> |    | Pin# |    | Description                                          |

|----------------|----------|----|------|----|------------------------------------------------------|

| Name           | Туре     | 40 | 42   | 44 | Description                                          |

| P1.0           | I/O      | 1  | 1    | 2  | General purpose I/O                                  |

| P1.1/HALFV     | I/O      | 2  | 2    | 3  | General purpose I/O / Vsync half frequency output.   |

| P1.2/HALFH     | I/O      | 3  | 3    | 4  | General purpose I/O / Hsync half frequency output.   |

| P1.3/HCLAMP    | I/O      | 4  | 4    | 5  | General purpose I/O / Hsync clamp pulse output.      |

| P1.4/AD2       | I/O      | 5  | 5    | 6  | General purpose I/O / ADC input.                     |

| P1.5/AD3       | I/O      | 6  | 6    | 8  | General purpose I/O / ADC input.                     |

| P1.6/AD0       | I/O      | 7  | 7    | 9  | General purpose I/O / ADC input                      |

| P1.7/AD1       | I/O      | 8  | 8    | 10 | General purpose I/O / ADC input                      |

| RST            | I        | 9  | 9    | 11 | Active high reset                                    |

| HSCL/P3.0/Rxd  | I/O      | 10 | 10   | 12 | IIC clock / General purpose I/O / Rxd                |

| HSDA/P3.1/Txd  | I/O      | 11 | 11   | 13 | IIC data / General purpose I/O / Txd                 |

| ISDA/P3.2/INT0 | I/O      | 12 | 12   | 14 | IIC data / General purpose I/O / INT0                |

| HSYNC          | I        | 13 | 13   | 15 | Horizontal SYNC or Composite SYNC                    |

| ISCL/P3.4/T0   | I/O      | 14 | 14   | 16 | IIC clock / General purpose I/O / T0                 |

| VSYNC          | I        | 15 | 15   | 17 | Vertical SYNC                                        |

| HCLAMP/P4.4    | 0        | -  | 16   | -  | Hsync clamp pulse output / General purpose output    |

| HBLANK/P4.1    | 0        | 16 | 17   | 19 | Horizontal blank / General purpose output            |

| VBLANK/P4.0    | 0        | 17 | 18   | 20 | Vertical blank / General purpose output              |

| X2             | 0        | 18 | 19   | 21 | Oscillator output                                    |

| X1             |          | 19 | 20   | 22 | Oscillator input                                     |

| VSS            | -        | 20 | 21   | 23 | Ground                                               |

| P2.0/INT0      | I/O      | 21 | 22   | 24 | General purpose I/O / INT0                           |

| P2.1           | I/O      | 22 | 23   | 25 | General purpose I/O                                  |

| P2.2           | I/O      | 23 | 24   | 26 | General purpose I/O                                  |

| P2.3           | I/O      | 24 | 25   | 27 | General purpose I/O                                  |

| DA13/P2.4      | I/O      | 25 | 26   | 28 | PWM DAC output / General purpose I/O (open-drain)    |

| DA12/P2.5      | I/O      | 26 | 27   | 30 | PWM DAC output / General purpose I/O (open-drain)    |

| DA11/P2.6      | I/O      | 27 | 28   | 31 | PWM DAC output / General purpose I/O (open-drain)    |

| DA10/P2.7      | I/O      | 28 | 29   | 32 | PWM DAC output / General purpose I/O (open-drain)    |

| STOUT/P4.2     | 0        | 29 | 30   | 33 | Self-test video output / General purpose output      |

| HALFH/P4.3     | 0        | -  | 31   | -  | Hsync half frequency output / General purpose output |

| DA9            | 0        | 30 | 32   | 34 | PWM DAC output / General purpose I/O (open-drain)    |

| DA8            | 0        | 31 | 33   | 35 | PWM DAC output / General purpose I/O (open-drain)    |

| DA7/P5.7       | 0        | 32 | 34   | 36 | PWM DAC output / General purpose I/O (open-drain)    |

| DA6/P5.6       | 0        | 33 | 35   | 37 | PWM DAC output / General purpose I/O (open-drain)    |

| DA5/P5.5       | 0        | 34 | 36   | 38 | PWM DAC output / General purpose I/O (open-drain)    |

| DA4/P5.4       | 0        | 35 | 37   | 39 | PWM DAC output / General purpose I/O (open-drain)    |

| DA3/P5.3       | 0        | 36 | 38   | 41 | PWM DAC output / General purpose I/O (open-drain)    |

| DA2/P5.2       | 0        | 37 | 39   | 42 | PWM DAC output / General purpose I/O (open-drain)    |

| DA1/P5.1       | 0        | 38 | 40   | 43 | PWM DAC output / General purpose I/O (open-drain)    |

| DA0/P5.0       | 0        | 39 | 41   | 44 | PWM DAC output / General purpose I/O (open-drain)    |

| VDD            | -        | 40 | 42   | 1  | Positive power supply                                |

# **3.0 FUNCTIONAL DESCRIPTION**

## 1.8051 CPU Core

MTV112A includes all 8051 functions with the following exceptions:

- 1.1 PSEN, ALE, RD and WR pins are disabled. The external RAM access is restricted to XFRs within MTV112A.

- 1.2 Port 0, port 3.3, and ports 3.5 ~ 3.7 are not general-purpose I/O ports. They are dedicated to monitor control or DAC pins.

- 1.3 INT1 and T1 input pins are not provided.

- 1.4 Ports 2.4 ~ 2.7 are shared with DAC pins; ports 3.0 ~ 3.2, and port3.4 are shared with monitor control pins.

In addition, there are 2 timers, 5 interrupt sources and a serial interface compatible with the standard 8051. The Txd/Rxd (P3.0/P3.1) pins are shared with DDC interface. INT0/T0 pins are shared with IIC interface. An extra option can be used to switch the INT0 source from P3.2 to P2.0. This feature maintains an external interrupt source when IIC interface is enabled.

# Note: All registers listed in this document reside in the external RAM area (XFR). For the internal RAM memory map please refer to the 8051 spec.

| Reg name | addr    | bit7  | bit6 | bit5 | bit4 | bit3  | bit2  | bit1  | bit0  |

|----------|---------|-------|------|------|------|-------|-------|-------|-------|

| PADMOD   | 30h (w) | SINT0 | IICF | DDCE | IICE | DA13E | DA12E | DA11E | DA10E |

| PADMOD   | 31h (w) | P57E  | P56E | P55E | P54E | P53E  | P52E  | P51E  | P50E  |

| PADMOD   | 37h (w) | -     | -    | -    | -    | -     | -     | -     | MORE  |

| SINT0 = | :1 -  | ightarrow INT0 source is pin #21.                          |

|---------|-------|------------------------------------------------------------|

| =       | 0 -   | $\rightarrow$ INT0 source is pin #12.                      |

| IICF =  | :1 -  | $\rightarrow$ Selects 400kHz master IIC speed.             |

| =       | 0 -   | $\rightarrow$ Selects 100kHz master IIC speed.             |

| DDCE =  | :1 -  | $\rightarrow$ Pin #10 is HSCL; pin #11 is HSDA.            |

| =       | - 0   | $\rightarrow$ Pin #10 is P3.0/Rxd; pin #11 is P3.1/Txd.    |

| IICE =  | :1 -  | ightarrow Pin #12 is ISDA; pin #14 is ISCL.                |

| =       | - 0   | $\rightarrow$ Pin #12 is P3.2/(INT0*); pin #14 is P3.4/T0. |

| DA13E = | :1 -  | $\rightarrow$ Pin #25 is DA13.                             |

| =       | - 0   | $\rightarrow$ Pin #25 is P2.4.                             |

| DA12E = | :1 -  | $\rightarrow$ Pin #26 is DA12.                             |

| =       | - 0   | $\rightarrow$ Pin #26 is P2.5.                             |

| DA11E = | :1 -  | $\rightarrow$ Pin #27 is DA11.                             |

| =       | - 0   | $\rightarrow$ Pin #27 is P2.6.                             |

| DA10E = | :1 -  | $\rightarrow$ Pin #28 is DA10.                             |

| =       | - 0   | $\rightarrow$ Pin #28 is P2.7.                             |

| P57E =  | :1 -  | $\rightarrow$ Pin #32 is P5.7.                             |

| =       | = 0 - | $\rightarrow$ Pin #32 is DA7.                              |

| P56E =  | :1 -  | $\rightarrow$ Pin #33 is P5.6.                             |

| =       | - 0   | $\rightarrow$ Pin #33 is DA6.                              |

| P55E =  | :1 -  | $\rightarrow$ Pin #34 is P5.5.                             |

| =       | = 0 - | $\rightarrow$ Pin #34 is DA5.                              |

| P54E =  | :1 -  | $\rightarrow$ Pin #35 is P5.4.                             |

| =       | = 0 - | $\rightarrow$ Pin #35 is DA4.                              |

| P53E =  | :1 -  | $\rightarrow$ Pin #36 is P5.3.                             |

| =       | = 0 - | $\rightarrow$ Pin #36 is DA3.                              |

| P52E =  | :1 -  | $\rightarrow$ Pin #37 is P5.2.                             |

| =       | = 0 - | $\rightarrow$ Pin #37 is DA2.                              |

- P51E = 1  $\rightarrow$  Pin #38 is P5.1.  $\rightarrow$  Pin #38 is DA1. = 0 P50E  $\rightarrow$  Pin #39 is P5.0. = 1  $\rightarrow$  Pin #39 is DA0. = 0MORE = 1→ Bits P57E, P56E, P55E, P54E, P53E, P52E, P51E, P50E, DACK, EHALFV, EHALFH, ENCLP, ADCMOD can be programmed, and master IIC speed is controlled by (MCLK1,MCLK0) bits.  $\rightarrow$  above bits internal keep "0" by MTV112A, and master IIC speed is controlled by = 0IICF bit.

- \* SINT0 should be 0 in this case.

## 2. Memory Allocation

#### 2.1 Internal Special Function Registers (SFR) SFR is a group of registers that is the same as standard 8051.

#### 2.2 Internal RAM

There is a 384 bytes RAM in MTV112A. The first portion of the RAM area contains 256 bytes, accessible by setting PSW.1=0; the second portion of the RAM area contains 128 bytes, accessible by setting PSW.1=1.

#### 2.3 External Special Function Registers (XFR)

XFR is a group of registers allocated in the 8051 external RAM area. Most of the registers are used for monitor control or PWM DAC. The program can initialize Ri value and use "MOVX" instruction to access these registers.

| FFH | Accessible by indirect<br>addressing only.<br>The value of PSW.1 = | SFR                                                 |     |                                                    |

|-----|--------------------------------------------------------------------|-----------------------------------------------------|-----|----------------------------------------------------|

|     | both 0 and 1.<br>(Using MOV A, @Ri                                 | Accessible by direct addressing.                    | FFH | XFR                                                |

| 80H | instruction)                                                       | Ū                                                   |     | Accessible by indirect<br>external RAM             |

| 7FH | Accessible by direct<br>and indirect<br>addressing.                | Accessible by direct<br>and indirect<br>addressing. | 00H | addressing.<br>(Using MOVX A, @Ri<br>Instruction.) |

| 00H | PSW.1=0                                                            | PSW.1 =1                                            |     |                                                    |

## 3. PWM DAC

Each D/A converter's output pulse width is controlled by an 8-bit register in XFR. The frequency of PWM clk is X'tal or 2 \* X'tal, selected by DACK. And the frequency of these DAC outputs is (PWM clk frequency)/253 or (PWM clk frequency)/256, selected by DIV253. If DIV253=1, writing FDH/FEH/FFH to the DAC register generates stable high output. If DIV253=0, the output will pulse low at least once even if the DAC register's content is FFH. Writing 00H to the DAC register generates stable low output.

| reg name | addr      | bit7              | bit6              | bit5              | bit4              | bit3              | bit2              | bit1              | bit0              |

|----------|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| DA0      | 20h (r/w) | DA0 <sub>b7</sub> | DA0b6             | DA0 <sub>b5</sub> | DA0 <sub>b4</sub> | DA0 <sub>b3</sub> | DA0 <sub>b2</sub> | DA0 <sub>b1</sub> | DA0 <sub>b0</sub> |

| DA1      | 21h (r/w) | DA1 <sub>b7</sub> | DA1 <sub>b6</sub> | DA1 <sub>b5</sub> | DA1 <sub>b4</sub> | DA1 <sub>b3</sub> | DA1 <sub>b2</sub> | DA1 <sub>b1</sub> | DA1 <sub>b0</sub> |

| DA2      | 22h (r/w) | DA2 <sub>b7</sub> | DA2 <sub>b6</sub> | DA2 <sub>b5</sub> | DA2 <sub>b4</sub> | DA2 <sub>b3</sub> | DA2 <sub>b2</sub> | DA2 <sub>b1</sub> | DA2 <sub>b0</sub> |

| DA3      | 23h (r/w) | DA3 <sub>b7</sub> | DA3 <sub>b6</sub> | DA3 <sub>b5</sub> | DA3 <sub>b4</sub> | DA3 <sub>b3</sub> | DA3 <sub>b2</sub> | DA3 <sub>b1</sub> | DA3 <sub>b0</sub> |

| DA4  | 24h (r/w) | DA4 <sub>b7</sub>  | DA4 <sub>b6</sub>  | DA4 <sub>b5</sub>  | DA4 <sub>b4</sub>  | DA4 <sub>b3</sub>  | DA4 <sub>b2</sub>  | DA4 <sub>b1</sub>  | DA4 <sub>b0</sub>  |

|------|-----------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| DA5  | 25h (r/w) | DA5 <sub>b7</sub>  | DA5 <sub>b6</sub>  | DA5 <sub>b5</sub>  | DA5 <sub>b4</sub>  | DA5 <sub>b3</sub>  | DA5 <sub>b2</sub>  | DA5 <sub>b1</sub>  | DA5 <sub>b0</sub>  |

| DA6  | 26h (r/w) | DA6 <sub>b7</sub>  | DA6 <sub>b6</sub>  | DA6 <sub>b5</sub>  | DA6 <sub>b4</sub>  | DA6 <sub>b3</sub>  | DA6 <sub>b2</sub>  | DA6 <sub>b1</sub>  | DA6 <sub>b0</sub>  |

| DA7  | 27h (r/w) | DA7 <sub>b7</sub>  | DA7 <sub>b6</sub>  | DA7 <sub>b5</sub>  | DA7 <sub>b4</sub>  | DA7 <sub>b3</sub>  | DA7 <sub>b2</sub>  | DA7 <sub>b1</sub>  | DA7 <sub>b0</sub>  |

| DA8  | 28h (r/w) | DA8 <sub>b7</sub>  | DA8 <sub>b6</sub>  | DA8 <sub>b5</sub>  | DA8 <sub>b4</sub>  | DA8 <sub>b3</sub>  | DA8 <sub>b2</sub>  | DA8 <sub>b1</sub>  | DA8 <sub>b0</sub>  |

| DA9  | 29h (r/w) | DA9 <sub>b7</sub>  | DA9 <sub>b6</sub>  | DA9 <sub>b5</sub>  | DA9 <sub>b4</sub>  | DA9 <sub>b3</sub>  | DA9 <sub>b2</sub>  | DA9 <sub>b1</sub>  | DA9 <sub>b0</sub>  |

| DA10 | 2Ah (r/w) | DA10 <sub>b7</sub> | DA10 <sub>b6</sub> | DA10 <sub>b5</sub> | DA10 <sub>b4</sub> | DA10 <sub>b3</sub> | DA10 <sub>b2</sub> | DA10 <sub>b1</sub> | DA10 <sub>b0</sub> |

| DA11 | 2Bh (r/w) | DA11 <sub>b7</sub> | DA11 <sub>b6</sub> | DA11 <sub>b5</sub> | DA11 <sub>b4</sub> | DA11 <sub>b3</sub> | DA11 <sub>b2</sub> | DA11 <sub>b1</sub> | DA11 <sub>b0</sub> |

| DA12 | 2Ch (r/w) | DA12 <sub>b7</sub> | DA12 <sub>b6</sub> |                    |                    | DA12 <sub>b3</sub> | DA12 <sub>b2</sub> | DA12 <sub>b1</sub> | DA12 <sub>b0</sub> |

| DA13 | 2Dh (r/w) | DA13 <sub>b7</sub> | DA13 <sub>b6</sub> | DA13 <sub>b5</sub> | DA13 <sub>b4</sub> | DA13 <sub>b3</sub> | DA13 <sub>b2</sub> | DA13 <sub>b1</sub> | DA13 <sub>b0</sub> |

| WDT  | 80h       | WEN                | WCLR               | CLRDDC             | DIV253             | DACK               | WDT2               | WDT1               | WDT0               |

| <b>DA0</b> (r/w) :  | The output pulse width control for DA0.                                     |

|---------------------|-----------------------------------------------------------------------------|

| <b>DA1</b> (r/w) :  | The output pulse width control for DA1.                                     |

| <b>DA2</b> (r/w) :  | The output pulse width control for DA2.                                     |

| <b>DA3</b> (r/w) :  | The output pulse width control for DA3.                                     |

| <b>DA4</b> (r/w) :  | The output pulse width control for DA4.                                     |

| <b>DA5</b> (r/w) :  | The output pulse width control for DA5.                                     |

| <b>DA6</b> (r/w) :  | The output pulse width control for DA6.                                     |

| <b>DA7</b> (r/w) :  | The output pulse width control for DA7.                                     |

| <b>DA8</b> (r/w) :  | The output pulse width control for DA8.                                     |

| <b>DA9</b> (r/w) :  | The output pulse width control for DA9.                                     |

| <b>DA10</b> (r/w) : | The output pulse width control for DA10.                                    |

| <b>DA11</b> (r/w) : | The output pulse width control for DA11.                                    |

| <b>DA12</b> (r/w) : | The output pulse width control for DA12.                                    |

| <b>DA13</b> (r/w) : | The output pulse width control for DA13.                                    |

| <b>WDT</b> (w) :    | Watchdog timer & special control bit.                                       |

| DIV253              | = 1 $\rightarrow$ The PWM DAC outputs frequency is (PWM clk frequency)/253. |

|                     | = 0 $\rightarrow$ The PWM DAC output frequency is Xtal frequency/256.       |

| DACK                |                                                                             |

|                     | $= 0 \rightarrow$ The PWM clk frequency is (X'tal frequency).               |

|                     |                                                                             |

\*1. All D/A converters are centered with value 80h after power-on.

#### 4. H/V SYNC Processing

The H/V SYNC processing block performs the functions of composite signal separation, SYNC input presence check, frequency counting, and polarity detection and control, as well as the protection of VBLANK output while VSYNC speeds up to a high DDC communication clock rate. The present and frequency function block treat any pulse less than one OSC period as noise.

#### 4.1 Composite SYNC Separation

MTV112A continuously monitors the input HSYNC. If the vertical SYNC pulse can be extracted from the input, a CVpre flag is set and the user can select the extracted "CVSYNC" for the source of polarity check, frequency count and VBLANK. The CVSYNC will have a 10-16 us delay compared to the original signal. The delay depends on the OSC frequency and composite mix method.

#### 4.2 H/V Frequency Counter

MTV112A can discriminate HSYNC/VSYNC frequency and saves the information in XFRs. The 15-bit Hcounter counts the time of the 64xHSYNC period, but only 11 upper bits are loaded into the HCNTH/HCNTL latch. The 11-bit output value is {2/H-Freq} / {1/OSC-Freq}, updated once per VSYNC/CVSYNC period when VSYNC/CVSYNC is present or continuously updated when VSYNC/CVSYNC is not present. The 14-bit Vcounter counts the time between 2 VSYNC pulses, but only 9 upper bits are

loaded into the VCNTH/VCNTL latch. The 9-bit output value is {1/V-Freq} / {512/OSC-Freq}, updated every VSYNC/CVSYNC period. An extra overflow bit indicates the condition of the H/V counter overflow. The VFchg/HFchg interrupt is active when VCNT/HCNT value changes or overflows. Tables 4.2.1 and 4.2.2 shows the HCNT/VCNT value under the operations of 8MHz and 12MHz.

## 4.2.1 H-Freq Table

| ы.  | Freq(KHZ) | Output Val           | ue (11 bits)          |

|-----|-----------|----------------------|-----------------------|

| 11- | req(Riz)  | 8MHz OSC (hex / dec) | 12MHz OSC (hex / dec) |

| 1   | 30        | 215h / 533           | 320h / 800            |

| 2   | 31.5      | 1FBh / 507           | 2F9h / 761            |

| 3   | 33.5      | 1DDh /477            | 2CCh / 716            |

| 4   | 35.5      | 1C2h / 450           | 2A4h / 676            |

| 5   | 36.8      | 1B2h / 434           | 28Ch / 652            |

| 6   | 38        | 1A5h / 421           | 277h / 631            |

| 7   | 40        | 190h / 400           | 258h / 600            |

| 8   | 48        | 14Dh / 333           | 1F4h / 500            |

| 9   | 50        | 140h / 320           | 1E0h / 480            |

| 10  | 57        | 118h / 280           | 1A5h / 421            |

| 11  | 60        | 10Ah / 266           | 190h / 400            |

| 12  | 64        | 0FAh / 250           | 177h / 375            |

| 13  | 100       | 0A0h / 160           | 0F0h / 240            |

- \*1. The H-Freq output (HF10 HF0) is valid.

- \*2. The tolerance deviation is  $\pm$  1 LSB.

## 4.2.2 V-Freq Table

| v  | -Freq(Hz) | Output Va            | lue (9 bits)          |

|----|-----------|----------------------|-----------------------|

| ľ  | -rieq(nz) | 8MHz OSC (hex / dec) | 12MHz OSC (hex / dec) |

| 1  | 56.25     | 115h / 277           | 1A0h / 416            |

| 2  | 59.94     | 104h / 260           | 187h / 391            |

| 3  | 60        | 104h / 260           | 186h / 390            |

| 4  | 60.32     | 103h / 259           | 184h / 388            |

| 5  | 60.53     | 102h / 258           | 183h / 387            |

| 6  | 66.67     | 0EAh / 234           | 15Fh / 351            |

| 7  | 70.069    | 0DEh / 222           | 14Eh / 334            |

| 8  | 70.08     | 0DEh / 222           | 14Eh / 334            |

| 9  | 72        | 0D9h /217            | 145h / 325            |

| 10 | 72.378    | 0D7h / 215           | 143h / 323            |

| 11 | 72.7      | 0D6h / 214           | 142h / 322            |

| 12 | 87        | 0B3h / 179           | 10Dh / 269            |

\*1. The V-Freq output (VF8 - VF0) is valid.

\*2. The tolerance deviation is  $\pm 1$  LSB.

#### 4.3 H/V Presence Check

The Hpresent function checks the input HSYNC pulse. The Hpre flag is set when HSYNC is over 10KHz or cleared when HSYNC is under 10Hz. The Vpresent function checks the input VSYNC pulse. The Vpre flag is set when VSYNC is over 40Hz or cleared when VSYNC is under 10Hz. A control bit "PREFS" selects the time base for these functions. The HPRchg interrupt is set when the Hpre value changes. The VPRchg interrupt is set when the Vpre/CVpre value changes. However, the CVpre flag interrupt may be disabled when S/W disables the composite function.

#### 4.4 H/V Polarity Detection

The polarity functions detect the input HSYNC/VSYNC high and low pulse duty cycle. If the high pulse duration is longer than that of the low pulse, the negative polarity is asserted; otherwise, positive polarity is asserted. The HPLchg interrupt is set when the Hpol value changes. The VPLchg interrupt is set when the Vpol value changes.

#### 4.5 Output HBLANK/VBLANK Control and Polarity Adjustment

The HBLANK is the mux output of HSYNC and self-test horizontal pattern. The VBLANK is the mux output of VSYNC, CVSYNC and the self-test vertical pattern. The mux selection and output polarity are S/W controllable. The VBLANK output is cut off when VSYNC frequency is over 200Hz or 133Hz depends on 8MHz/12MHz OSC selection. The HBLANK/VBLANK shares the output pin with P4.1/ P4.0.

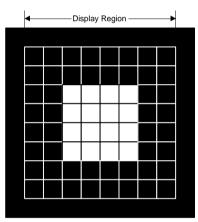

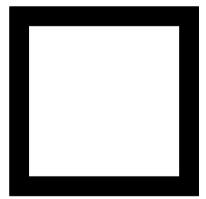

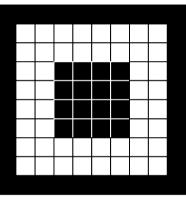

#### 4.6 Self-Test Pattern Generator

This generator can generate 4 display patterns for testing purposes: positive cross-hatch, negative cross-hatch, full white, and full black (shown in the following figure). It was originally designed to support the monitor manufacturer in performing a burn-in test, or to offer the end-user a reference to check the monitor. The generator's output STOUT shares the output pin with P4.2.

**Positive Cross-Hatch**

Full White

**Negative Cross-Hatch**

Full Black

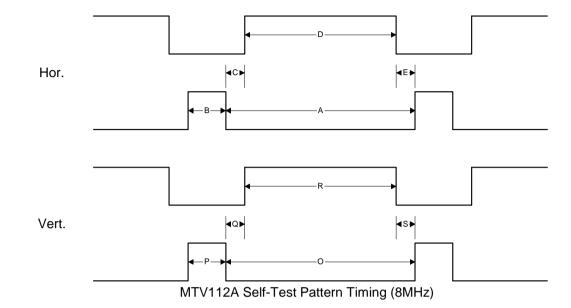

|                  | 63.5KHz, 6    | 60Hz   | 31.7KHz, 6    | 0Hz    |

|------------------|---------------|--------|---------------|--------|

|                  | Absolute time | H dots | Absolute time | H dots |

| Hor. Total Time  | Us(A)=15.75   | 1280   | Us(A)=31.5    | 640    |

| Hor. Acitve Time | Us(D)=12.05   | 979.3  | Us(D)=24.05   | 488.6  |

| Hor. F. P.       | Us(E)=0.2     | 16.25  | Us(E)=0.45    | 9      |

| SYNC Pulse Width | Us(B)=1.5     | 122    | Us(B)=3       | 61     |

| Hor. B. P.       | Us(C)=2       | 162.54 | Us(C)=4       | 81.27  |

|                  | V lines       | 6      | V lines       |        |

| Hor. Total Time  | Us(O)=16.6635 | 1024   | Us(O)=16.6635 | 480    |

| Hor. Active Time | Us(R)=15.6555 | 962    | Us(R)=15.6555 | 451    |

| Hor. F. P.       | Us(S)=0.063   | 3.87   | Us(S)=0.063   | 1.82   |

| SYNC Pulse Width | Us(P)=0.063   | 3.87   | Us(P)=0.063   | 1.82   |

| Hor. B. P.       | Us(Q)=0.882   | 54.2   | Us(Q)=0.882   | 25.4   |

\* 8 x 8 blocks of cross-hatch pattern in display region.

#### 4.7 VSYNC Interrupt

MTV112A checks the VSYNC input pulse and generates an interrupt at its leading edge. The VSYNC1 flag is set each time MTV112A detects a VSYNC pulse.

| reg name | addr    | bit7  | bit6  | bit5  | bit4   | bit3  | bit2  | bit1   | bit0   |

|----------|---------|-------|-------|-------|--------|-------|-------|--------|--------|

| PSTUS    | 40h (r) | CVpre | Х     | Hpol  | Vpol   | Hpre  | Vpre  | Hoff   | Voff   |

| HCNTH    | 41h (r) | Hovf  | Х     | Х     | Х      | Х     | HF10  | HF9    | HF8    |

| HCNTL    | 42h (r) | HF7   | HF6   | HF5   | HF4    | HF3   | HF2   | HF1    | HF0    |

| VCNTH    | 43h (r) | Vovf  | Х     | Х     | Х      | Х     | Х     | Х      | VF8    |

| VCNTL    | 44h (r) | VF7   | VF6   | VF5   | VF4    | VF3   | VF2   | VF1    | VF0    |

| PCTR0    | 40h (w) | C1    | C0    | HVsel | STOsel | PREFS | HALFV | HBpl   | VBpl   |

| PCTR2    | 42h (w) | Х     | Х     | Х     | Selft  | STbsh | Rt1   | Rt0    | STF    |

| PCTR3    | 43h (w) | ENCLP | CLPEG | CLPPO | CLPW2  | CLPW1 | CLPW0 | EHALFV | EHALFH |

| P4OUT    | 44h (w) | Х     | Х     | Х     | P44    | P43   | P42   | P41    | P40    |

#### 4.8 H/V SYNC Processor Register

| P5OUT  | 45h (r/w) | P57    | P56    | P55    | P54    | P53   | P52   | P51    | P50      |

|--------|-----------|--------|--------|--------|--------|-------|-------|--------|----------|

| PCTR6  | 46h (w)   | Х      | Х      | Х      | Х      | Х     | Х     | CLPsel | HALFHsel |

| INTFLG | 50h (r/w) | HPRchg | VPRchg | HPLchg | VPLchg | HFchg | VFchg | FIFOI  | MI       |

| INTEN  | 60h (w)   | EHPR   | EVPR   | EHPL   | EVPL   | EHF   | EVF   | EFIFO  | EMI      |

| INTFLG | 51h(r/w)  | Х      | Х      | Х      | Х      | Х     | Х     | Х      | VSYNC    |

| INTEN  | 61h(w)    | Х      | Х      | Х      | Х      | Х     | Х     | Х      | EVSI     |

H/V SYNC Processor Block Diagram

**PSTUS** (r) : The status of polarity, presence and static level for HSYNC and VSYNC.

= 1  $\rightarrow$  The extracted CVSYNC is present. CVpre = 0  $\rightarrow$  The extracted CVSYNC is not present.  $\rightarrow$  HSYNC input is positive polarity. Hpol = 1  $\rightarrow$  HSYNC input is negative polarity. = 0 $\rightarrow$  VSYNC (CVSYNC) is positive polarity. Vpol = 1  $\rightarrow$  VSYNC (CVSYNC) is negative polarity. = 0 $\rightarrow$  HSYNC input is present. Hpre = 1  $\rightarrow$  HSYNC input is not present. = 0Vpre  $\rightarrow$  VSYNC input is present. = 1 = 0 $\rightarrow$  VSYNC input is not present. Hoff\* = 1  $\rightarrow$  HSYNC input's off-level is high. = 0  $\rightarrow$  HSYNC input's off-level is low.  $\rightarrow$  VSYNC input's off-level is high. Voff\* = 1  $\rightarrow$  VSYNC input's off-level is low. = 0

\*Hoff and Voff are valid when Hpre=0 or Vpre=0.

**HCNTH** (r) : H-Freq counter's high bits.

| Hovf | = 1 | $\rightarrow$ H-Freq counter overflows; this bit is cleared by H/W when condition removed. |

|------|-----|--------------------------------------------------------------------------------------------|

|------|-----|--------------------------------------------------------------------------------------------|

HF10 - HF8 : 3 high bits of H-Freq counter.

**HCNTL** (r) : H-Freq counter's low bits.

| VCNTH (r) : | V-Freq counter's high bits. |

|-------------|-----------------------------|

|-------------|-----------------------------|

- Vovf = 1  $\rightarrow$  V-Freq counter overflows; this bit is cleared by H/W when condition removed. VF8 : High bit of V-Freq counter.

- **VCNTL** (r) : V-Freq counter's low bits.

| PCTR0 | (w) :<br>C1, C0               |                                                           | processor control register 0.<br>$\rightarrow$ Selects CVSYNC as the polarity, Freq and VBLANK source.<br>$\rightarrow$ Selects VSYNC as the polarity, Freq and VBLANK source.<br>$\rightarrow$ Disables composite function (MTV012 compatible mode).<br>$\rightarrow$ H/W auto switches to CVSYNC when CVpre=1 and VSpre=0. |  |  |  |  |  |

|-------|-------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | HVsel                         | IVsel = 1 $\rightarrow$ Pin #16 is P4.1, pin #17 is P4.0. |                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|       | STOse                         | = 0<br>  = 1                                              | $\rightarrow$ Pin #16 is HBLANK, pin #17 is VBLANK.<br>$\rightarrow$ Pin #29 is P4.2.                                                                                                                                                                                                                                        |  |  |  |  |  |

|       | PREFS<br>HALFV                | = 1                                                       | → Pin #29 is STOUT.<br>→ Selects 8MHz OSC as H/V presence check and self-test pattern time base.<br>→ Selects 12MHz OSC as H/V presence check and self-test pattern time base.                                                                                                                                               |  |  |  |  |  |

|       |                               | = 1                                                       | $\rightarrow$ VBLANK is half frequency output of VSYNC.<br>$\rightarrow$ Negative polarity HBLANK output.                                                                                                                                                                                                                    |  |  |  |  |  |

|       |                               | = 0                                                       | $\rightarrow$ Positive polarity HBLANK output.                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|       | VBpl                          | = 1                                                       | $\rightarrow$ Negative polarity VBLANK output.                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|       |                               | = 0                                                       | $\rightarrow$ Positive polarity VBLANK output.                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| PCTR2 | (w) :                         | Self-tes                                                  | st pattern generator control.                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|       | Selft                         | = 1                                                       | $\rightarrow$ Enables generator.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|       | от                            | = 0                                                       | $\rightarrow$ Disables generator.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|       | STbsh                         | = 1<br>= 0                                                | $\rightarrow$ 63.5KHz (horizontal) output selected.<br>$\rightarrow$ 31.75KHz (horizontal) output selected.                                                                                                                                                                                                                  |  |  |  |  |  |

|       | = 0<br>Rt1, Rt0= 0,0<br>= 0,1 |                                                           | $\rightarrow$ S1.75KHz (nonzonial) output selected.<br>$\rightarrow$ Positive cross-hatch pattern output.                                                                                                                                                                                                                    |  |  |  |  |  |

|       |                               |                                                           | $\rightarrow$ Negative cross-hatch pattern output.                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|       |                               | = 1,0                                                     | $\rightarrow$ Full white pattern output.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|       |                               | = 1,1                                                     | $\rightarrow$ Full black pattern output.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|       | STF                           | = 1                                                       | $\rightarrow$ Enables STOUT output.                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|       |                               | = 0                                                       | $\rightarrow$ Disables STOUT output.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| PCTR3 | . ,                           |                                                           | C clamp pulse control register.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|       | ENCLP                         |                                                           | $\rightarrow$ pin #4 is HCLAMP.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|       | CLPEG                         | = 0<br>: - 1                                              | $\rightarrow$ pin #4 is P1.3.<br>$\rightarrow$ Clamp pulse follows HSYNC leading edge.                                                                                                                                                                                                                                       |  |  |  |  |  |

|       |                               | = 0                                                       | $\rightarrow$ Clamp pulse follows HSYNC trailing edge.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|       | CLPPO                         | -                                                         | $\rightarrow$ Positive polarity clamp pulse output.<br>$\rightarrow$ Negative polarity clamp pulse output.                                                                                                                                                                                                                   |  |  |  |  |  |

|       |                               | = 0                                                       |                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|       |                               |                                                           | V0 : Pulse width of clamp pulse is<br>[(CLPW2:CLPW0) + 1] X 0.25 μs for 8MHz X'tal selection,or<br>[(CLPW2:CLPW0) + 1] X 0.167 μs for 12MHz X'tal selection.                                                                                                                                                                 |  |  |  |  |  |

|       | EHALF                         |                                                           | $\rightarrow$ pin #2 is HALFV.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|       |                               | = 0                                                       | $\rightarrow$ pin #2 is P1.1.                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|       | EHALF                         |                                                           | $\rightarrow$ pin #3 is HALFH.<br>$\rightarrow$ pin #3 is P1.2.                                                                                                                                                                                                                                                              |  |  |  |  |  |

|       |                               | = 0                                                       | → µווו +ט ט ד 1.2.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| P4OUT | (w) :                         | Port 4 d                                                  | data output value.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

**P5OUT** (r/w) : Port 5 data input/output value.

| PCTR6 (w) :  | Sync processor control register 6.                                                                                                                                                                                                                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLPse        | $H = 1 \rightarrow \text{pin HCLAMP/P4.4 is P4.4.}$                                                                                                                                                                                                        |

|              | = 0 $\rightarrow$ pin HCLAMP/P4.4 is HCLAMP.                                                                                                                                                                                                               |

| HALFH        | Hsel = 1 $\rightarrow$ pin HALFH/P4.3 is P4.3.                                                                                                                                                                                                             |

|              | = 0 $\rightarrow$ pin HALFH/P4.3 is HALFH.                                                                                                                                                                                                                 |

| INTFLG (w) : | Interrupt flag. An interrupt event will set its individual flag, and, if the corresponding interrupt enabler bit is set, the 8051 core's INT1 source will be driven by a zero level. Software MUST clear this register while serving the interrupt routine |

| oicui     | the register while serving the interrupt routine  |

|-----------|---------------------------------------------------|

| HPRchg= 1 | $\rightarrow$ No action.                          |

| = 0       | ightarrow Clears HSYNC presence change flag.      |

| VPRchg= 1 | $\rightarrow$ No action.                          |

| = 0       | ightarrow Clears VSYNC presence change flag.      |

| HPLchg= 1 | $\rightarrow$ No action.                          |

| = 0       | ightarrow Clears HSYNC polarity change flag.      |

| VPLchg=1  | $\rightarrow$ No action.                          |

| = 0       | ightarrow Clears VSYNC polarity change flag.      |

| HFchg = 1 | $\rightarrow$ No action.                          |

| = 0       | $\rightarrow$ Clears HSYNC frequency change flag. |

| VFchg = 1 | $\rightarrow$ No action.                          |

| = 0       | $\rightarrow$ Clears VSYNC frequency change flag. |

| VSYNCi= 1 | $\rightarrow$ No action.                          |

| = 0       | ightarrow Clears VSYNC interrupt flag.            |

**INTFLG** (r) : Interrupt flag.

| (.).      |                                                                        |

|-----------|------------------------------------------------------------------------|

| HPRchg= 1 | ightarrow Indicates an HSYNC presence change.                          |

| VPRchg= 1 | ightarrow Indicates a VSYNC presence change.                           |

| HPLchg= 1 | ightarrow Indicates a HSYNC polarity change.                           |

| VPLchg=1  | ightarrow Indicates a VSYNC polarity change.                           |

| HFchg = 1 | $\rightarrow$ Indicates an HSYNC frequency change or counter overflow. |

| VFchg = 1 | $\rightarrow$ Indicates a VSYNC frequency change or counter overflow.  |

| VSYNCi= 1 | $\rightarrow$ Indicates a VSYNC interrupt.                             |

|           |                                                                        |

**INTEN** (w) : Interrupt enabler.

| <b>`</b> |     |                                                                            |

|----------|-----|----------------------------------------------------------------------------|

| EHPR     | = 1 | ightarrow Enables HSYNC presence change interrupt.                         |

| EVPR     | = 1 | ightarrow Enables VSYNC presence change interrupt.                         |

| EHPL     | = 1 | ightarrow Enables HSYNC polarity change interrupt.                         |

| EVPL     | = 1 | ightarrow Enables VSYNC polarity change interrupt.                         |

| EHF      | = 1 | $\rightarrow$ Enables HSYNC frequency change / counter overflow interrupt. |

| EVF      | = 1 | $\rightarrow$ Enables VSYNC frequency change / counter overflow interrupt. |

| EVSI     | = 1 | $\rightarrow$ Enables VSYNC interrupt.                                     |

|          |     |                                                                            |

## 5. DDC & IIC Interface

## 5.1 DDC1 Mode

MTV112A enters DDC1 mode after Reset. In this mode, VSYNC is used as a data clock. The HSCL pin should remain at high. The data output to the HSDA pin is taken from 8 bytes f FIFO in MTV112A. MTV112A fetches the data byte from FIFO, then sends it in a 9-bit packet format which includes a null bit (=1) as packet separator. The software program should load EDID data (original stored in EEPROM) into FIFO and take care of the FIFO depth. FIFO sets the FIFOI (FIFO low interrupt) flag when there are fewer than N (N=2,3,4 or 5 controlled by LS1, LS0) bytes to be output to the HSDA pin. To prevent FIFO from emptying, software needs to write EDID data to FIFO as soon as FIFOI is set. On the other hand, FIFO sets the FIFOH flag when its capacity is full. Software should not write additional data to FIFO in such instance. The FIFOI interrupt can be masked or enabled by an EFIFO control bit. A simple way to control FIFO is to set (LS1, MTV112A Revision 1.9 05/18/2001

LS0=1,0) and enable FIFOI interrupt, then software may load 4 bytes into FIFO each time a FIFOI interrupt arises. A special control bit "LDFIFO" can reduce the software effort when EDID data is stored in EEPROM. If LDFIFO=1, FIFO will be automatically loaded with MBUF data when software reads MBUF XFR.

#### 5.2 DDC2B Mode

MTV112A switches to DDC2B mode when it detects a high to low transition on the HSCL pin. Once MTV112A enters DDC2B mode, the host can access the EEPROM using IIC bus protocol as if the HSDA and HSCL are directly bypassed to ISDA and ISCL pins. MTV112A will return to DDC1 mode if HSCL is kept high for a 128 VSYNC clock period. However, it will lock in DDC2B mode if a valid IIC access has been detected on HSCL/HSDA bus. The DDC2 flag reflects the current DDC status. S/W may clear it by setting CLRDDC. Control bits M128/M256 are used to block the EEPROM write operation from the host if the address is over 128/256.

#### 5.3 Master Mode IIC Function Block

The master mode IIC block is connected to the ISDA and ISCL pins. Its speed can be selected to 100kHz or 400kHz by s/w set IICF control bit while MORE=0, or to 50KHz,100KHz,200KHz or 400KHz by s/w set (MCLK1,MCLK0) bits while MORE=1. The software program can access the external EEPROM through this interface. Since the EDID/VDIF data and display information share the common EEPROM, precaution must be taken to avoid bus conflict. In DDC1 mode, the IIC interface is controlled by MTV112A only. In DDC2B mode, the host may access the EEPROM directly. Software can test the HSCL condition by reading the BUSY flag, which is set in case HSCL=0. A summary of master IIC access is illustrated as follows:

#### 5.3.1. To Write EEPROM

- 1. Write the EEPROM slave address to MBUF (bit 0 = 0).

- 2. Set the S bit to Start.

- 3. After MTV112A transmits this byte, an MI interrupt will be triggered.

- 4. The program can write MBUF to transfer the next byte or set the P bit to Stop.

- \* Please see the attachments about "Master IIC Transmission Timing".

## 5.3.2. To Read EEPROM

- 1. Write the slave address to MBUF (bit 0 = 1).

- 2. Set the S bit to Start.

- 3. After MTV112A transmits this byte, a MI interrupt will be triggered.

- 4. Set or reset the ACK flag according to the IIC protocol.

- 5. Read out the useless byte to MBUF to continue the data transfer.

- 6. After MTV112A receives a new byte, the MI interrupt is triggered again.

- 7. Reading MBUF also triggers the next receiving operation, but setting the P bit before reading can terminate the operation.

- \* Please see the attachments about "Master IIC Timing Receiving".

#### 5.4 Slave Mode IIC Function Block

The slave mode IIC block can be connected to HSDA/HSCL or ISDA/ISCL pins, and selected by the SLVsel control bit. This block can receive/transmit data using the IIC protocol. S/W may set the SLVADR register to determine which slave address the block should respond to.

In receiving mode, the block first detects an IIC slave address match condition then issues a SLVMI interrupt. The data received from SDA is shifted into a shift register and written to the RCBUF latch. The first byte loaded is the word address (slave address is dropped). This block also generates an RCBI (Receive Buffer full Interrupt) each time the RCBUF is loaded. If S/W can't read out the RCBUF in time, the next byte will not be written to RCBUF and the slave block will return NACK to the master. This feature guarantees the data integrity of communication. A WADR flag can tell S/W if the data in RCBUF is a word address.

In transmission mode, the block first detects an IIC slave address match condition then issues a SLVMI. In the meantime, the data pre-stored in the TXBUF is loaded into the shift register, results in TXBUF emptying and generates a TXBI (Transmission Buffer Interrupt). S/W should write the TXBUF a new byte for the next transfer before the shift register empties. Failure to do this will cause data corruption. The TXBI occurs each time the shift register receives new data from TXBUF. The SLVMI is cleared by writing the SLVSTUS register. The RCBI is cleared by reading the RCBUF. The TXBI is cleared by writing the TXBUF.

If the control bit ENSCL is set, the block will hold SCL low until the RCBI/TXBI is cleared.

\*Please see the attachments about "Slave IIC Block Timing".

| Reg name | addr      | bit7    | bit6    | bit5    | bit4        | bit3     | bit2    | bit1    | bit0   |

|----------|-----------|---------|---------|---------|-------------|----------|---------|---------|--------|

| MCTR     | 00h (w)   | LS1     | LS0     | LDFIFO  | M256        | M128     | ACK     | Р       | S      |

| MSTUS    | 00h (r)   | Х       | SCLERR  | DDC2    | BERR        | HFREQ    | FIFOH   | FIFOL   | BUSY   |

| MCTR     | 01h (w)   | Х       | Х       | Х       | Х           | Х        | Х       | MCLK1   | MCLK0  |

| MBUF     | 10h (r/w) | MBUF7   | MBUF6   | MBUF5   | MBUF4       | MBUF3    | MBUF2   | MBUF1   | MBUF0  |

| INTFLG   | 50h (r/w) | HPRchg  | VPRchg  | HPLchg  | VPLchg      | HFchg    | VFchg   | FIFOI   | MI     |

| INTEN    | 60h (w)   | EHPR    | EVPR    | EHPL    | EVPL        | EHF      | EVF     | EFIFO   | EMI    |

| FIFO     | 70h (w)   | FIFO7   | FIFO6   | FIFO5   | FIFO4       | FIFO3    | FIFO2   | FIFO1   | FIFO0  |

| SLVCTR   | 90h (w)   | ENSLV   | SLVsel  | ERCBI   | ESLVMI      | ETXBI    | ENSCL   | Х       | Х      |

| SLVSTUS  | 91h (r)   | WADR    | SLVS    | RCBI    | SLVMI       | TXBI     | RWB     | ACKIN   | Х      |

| SLVSTUS  | 91h (w)   |         |         | ١       | Write to cl | ear SLVM |         |         |        |

| RCBUF    | 92h (r)   | RCbuf7  | RCbuf6  | RCbuf5  | RCbuf4      | RCbuf3   | RCbuf2  | RCbuf1  | RCbuf0 |

| TXBUF    | 92h (w)   | TXbuf7  | TXbuf6  | TXbuf5  | TXbuf4      | TXbuf3   | TXbuf2  | TXbuf1  | TXbuf0 |

| SLVADR   | 93h (w)   | SLVadr7 | SLVadr6 | SLVadr5 | SLVadr4     | SLVadr3  | SLVadr2 | SLVadr1 | Х      |

MCTR (w) : Master IIC interface control register.

| ( <i>)</i>         |           | 5                                                                       |

|--------------------|-----------|-------------------------------------------------------------------------|

| LS1, LS0           | = 11      | $\rightarrow$ FIFOL is the status in which FIFO depth < 5.              |

|                    | = 10      | $\rightarrow$ FIFOL is the status in which FIFO depth < 4.              |

|                    | = 01      | $\rightarrow$ FIFOL is the status in which FIFO depth < 3.              |

|                    | = 00      | $\rightarrow$ FIFOL is the status in which FIFO depth < 2.              |

| LDFIFO             | = 1       | $\rightarrow$ FIFO will be written while S/W reads MBUF.                |

| M256               | = 1       | $\rightarrow$ Disables host writing EEPROM when address is over 256.    |

| M128               | = 1       | $\rightarrow$ Disables host writing EEPROM when address is over 128.    |

| ACK                | = 1       | $\rightarrow$ In receiving mode, no acknowledgment is given by MTV112A. |

|                    | = 0       | $\rightarrow$ In receiving mode, ACK is returned by MTV112A.            |

| S, P               | = ↑, 0    | $\rightarrow$ Start condition when Master IIC is not transferring.      |

|                    | = X, ↑    | $\rightarrow$ Stop condition when Master IIC is not transferring.       |

|                    | = 1, X    | $\rightarrow$ Will resume transfer after a read/write MBUF operation.   |

|                    | = X, 0    | $\rightarrow$ Forces HSCL low and occupies the IIC bus.                 |

| MCLK1 : MCLI       | K0 : Mast | er IIC speed select,                                                    |

|                    | = 0       | ightarrow 50KHz for 8MHz X'tal, 75KHz for 12MHz X'tal.                  |

|                    | = 1       | ightarrow 100KHz for 8MHz X'tal, 150KHz for 12MHz X'tal.                |

|                    | = 2       | ightarrow 200KHz for 8MHz X'tal, 300KHz for 12MHz X'tal .               |

|                    | = 3       | ightarrow 400KHz for 8MHz X'tal, 600KHz for 12MHz X'tal.                |

|                    |           | lock to sample the S/P bit; any pulse should sustain at least 20us.     |

| A write/read widdr | operatio  | n can be recognized only after 10us of the MI flag's rising edge.       |

| MSTUS (r) : | Master IIC inter | face status register.                                                                                               |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------|

| SCLEF       | RR = 1           | $\rightarrow$ The ISCL pin has been pulled low by other devices during the transfer, cleared when S=0.              |

| DDC2        | = 1              | $\rightarrow$ DDC2B is active.                                                                                      |

|             | = 0              | $\rightarrow$ MTV112A remains in DDC1 mode.                                                                         |

| BERR        | = 1              | $\rightarrow$ IIC bus error, no ACK received from the slave, updated each time the slave sends ACK on the ISDA pin. |

| HFREC       | ຊ = 1            | $\rightarrow$ MTV112A has detected a higher than 200Hz clock on the VSYNC pin.                                      |

| FIFOH       | = 1              | $\rightarrow$ FIFO high indicated.                                                                                  |

| FIFOL       | = 1              | $\rightarrow$ FIFO low indicated.                                                                                   |

| BUSY        | = 1              | ightarrow Host drives the HSCL pin to low.                                                                          |

\* While writing FIFO, the FIFOH/FIFOL flag will reflect the FIFO condition after 30us.

- **MBUF** (w) : Master IIC data shift register, after START and before STOP condition, write this register will resume MTV112A's transmission to the IIC bus.

- **MBUF** (r) : Master IIC data shift register, after START and before STOP condition, read this register will resume MTV112A's receiving from the IIC bus.

- **INTFLG** (w) : Interrupt flag. An interrupt event will set its individual flag, and, if the corresponding interrupt enabler bit is set, the 8051 INT1 source will be driven by a zero level. Software MUST clear this register while serving the interrupt routine.

- FIFOI = 1  $\rightarrow$  No action.

- $= 0 \rightarrow \text{Clears FIFOI flag.}$

- MI = 1  $\rightarrow$  No action.

- $= 0 \rightarrow$  Clears Master IIC bus interrupt flag (MI).

- **INTFLG** (r) : Interrupt flag.

- FIFOI = 1  $\rightarrow$  Indicates the FIFO low condition; when EFIFO is set, MTV112A will be interrupted by INT1.

- MI = 1  $\rightarrow$  Indicates when a byte is sent/received to/from the IIC bus; when EME is active, MTV112A will be interrupted by INT1.

- **INTEN** (w) : Interrupt enabler.

- EFIFO = 1  $\rightarrow$  Enables FIFO interrupt.

- EMI = 1  $\rightarrow$  Enables Master IIC bus interrupt.

- **FIFO** (w) : Writes FIFO contents.

**SLVCTR** (w) : Slave IIC block control.

| ENSLV  | = 1 | $\rightarrow$ Enables slave IIC block.                     |

|--------|-----|------------------------------------------------------------|

|        | = 0 | ightarrow Disables slave IIC block.                        |

| SLVsel | = 1 | $\rightarrow$ Slave IIC connects to ISDA/ISCL.             |

|        | = 0 | $\rightarrow$ Slave IIC connects to HSDA/HSCL.             |

| ERCBI  | = 1 | $\rightarrow$ Enables slave receiving buffer interrupt.    |

| ESLVMI | = 1 | $\rightarrow$ Enables slave address match interrupt.       |

| ETXBI  | = 1 | $\rightarrow$ Enables slave transmission buffer interrupt. |

| ENSCL  | = 1 | $\rightarrow$ Enables slave block to hold SCL pin low.     |

|        |     |                                                            |

**SLVSTUS** (r) : Slave IIC block status.

| WADR  | = 1 | ightarrow The data in SLVBUF is a word address.                                                      |

|-------|-----|------------------------------------------------------------------------------------------------------|

| SLVS  | = 1 | ightarrow The slave block has detected a START; cleared when STOP detected.                          |

| RCBI  | = 1 | ightarrow RCBUF has loaded a new data byte; reset by S/W reading RCBUF.                              |

| SLVMI | = 1 | → The slave block has detected the slave address match condition; cleared<br>by S/W writing SLVSTUS. |

| TXBI  | = 1 | $\rightarrow$ TXBUF is empty; reset by S/W writing TXBUF.                                            |

| RWB   | = 1 | $\rightarrow$ Current transfer is slave transmitting.                                                |

|       | = 0 | ightarrow Current transfer is slave receiving.                                                       |

| ACKIN | = 1 | ightarrow Master responds to NACK.                                                                   |

|       |     |                                                                                                      |

**SLVSTUS** (w) : Clears SLVMI flag.

- **RCBUF** (r) : Slave IIC receives data buffer.

- **TXBUF** (w) : Slave IIC transmits data buffer.

SLVADR (w): Slave IIC address to which the slave block should respond.

## 6. Low Power Reset (LVR) & Watchdog Timer

When the voltage level of the power supply is below 4.0V for a specific time, the LVR will generate a chip resetting signal. After the power supply is above 4.0V, LVR maintains the reset state for 144 Xtal cycles to guarantee the chip exit reset condition has a stable Xtal oscillation. The specific time of power supply in a low level is 3us and is adjustable by an external capacitor connected to the RST pin.

The watchdog timer automatically generates a device reset when it overflows. The interval of overflow is 0.25 sec x N, in which N is a number from 1 to 8, and can be programmed via register WDT (2:0). The timer function is disabled after power-on reset. The user can activate this function by setting WEN and clear the timer by setting WCLR.

## 7. A/D Converter

WEN

The MTV112 is equipped with two 4-bit or four 6-bit A/D converters. Each one can be enabled/disabled by S/W control. The refresh rate for the ADC is OSC freq./6144(4-bit) or OSC freq./12288(6-bit). The ADC compare the input pin voltage with the internal VDD\*N/16(4-bit) or VDD\*N/64(6-bit) voltage (where N = 0 -15 or N = 0 - 63). The ADC output value is N when pin voltage is greater than VDD\*N/16 or VDD N/64 and smaller than VDD\*(N+1)/16 or VDD\*(N+1)/64.

| Reg name | addr    | bit7  | bit6  | bit5   | bit4   | bit3  | bit2  | bit1  | bit0  |

|----------|---------|-------|-------|--------|--------|-------|-------|-------|-------|

| ADC      | A0h (w) | ENADC | Х     | Х      | Х      | Х     | Х     | EADC1 | EADC0 |

| ADC      | A0h (r) | AD1b3 | AD1b2 | AD1b1  | AD1b0  | AD0b3 | AD0b2 | AD0b1 | AD0b0 |

| ADC      | A0h (r) | Х     | Х     | ADb5   | ADb4   | ADb3  | ADb2  | ADb1  | ADb0  |

| WDT      | 80h (w) | WEN   | WCLR  | CLRDDC | DIV253 | DACK  | WDT2  | WDT1  | WDT0  |

$\rightarrow$  Enables watchdog timer.

**WDT** (w) : Watchdog timer control register. = 1

|                  | -       | ·                                                          |

|------------------|---------|------------------------------------------------------------|

| WCLR             | = 1     | ightarrow Clears watchdog timer.                           |

| CLRDDC           | = 1     | ightarrow Clears DDC2 flag.                                |

| WDT2: WDT0       | = 0     | $\rightarrow$ Overflow interval = 8 x 0.25 sec.            |

|                  | = 1     | $\rightarrow$ Overflow interval = 1 x 0.25 sec.            |

|                  | = 2     | $\rightarrow$ Overflow interval = 2 x 0.25 sec.            |

|                  | = 3     | $\rightarrow$ Overflow interval = 3 x 0.25 sec.            |

|                  | = 4     | $\rightarrow$ Overflow interval = 4 x 0.25 sec.            |

|                  | = 5     | $\rightarrow$ Overflow interval = 5 x 0.25 sec.            |

|                  | = 6     | $\rightarrow$ Overflow interval = 6 x 0.25 sec.            |

|                  | = 7     | $\rightarrow$ Overflow interval = 7 x 0.25 sec.            |

|                  |         |                                                            |

| ADC (w) : ADC co | ontrol. |                                                            |

| ENADC            | = 1     | $\rightarrow$ Enables ADC.                                 |

| ADCMOD           | = 1     | $\rightarrow$ 4 channels 6 bits ADC are selected.          |

|                  |         | Note: Only one ADC input can be enabled at the same time.  |

|                  | = 0     | $\rightarrow$ Dual 4 bits ADC are selected.(ADC1 and ADC0) |

| EADC3            | = 1     | ightarrow Enables ADC3 pin input.                          |

| EADC2            | = 1     | $\rightarrow$ Enables ADC2 pin input.                      |

| EADC1            | = 1     | $\rightarrow$ Enables ADC1 pin input.                      |

| EADC0            | = 1     | $\rightarrow$ Enables ADC0 pin input.                      |

|                  |         |                                                            |

ADC conversion result. **ADC** (r) :

AD1b3: AD1b0 4-bit ADC1 convert result. AD0b3: AD0b0 4-bit ADC0 convert result.

ADb5: ADb0 6-bit ADC convert result.

# 4.0 Test Mode Condition

In normal applications, users should avoid the MTV012 entering its test/program mode, outlined as follow: Test Mode A: RESET=1 & DA9=0 & DA8=1 & DA7=1 & DA6=0 Test Mode B: RESET falling edge & DA9=1 & DA8=0 & DA7=1 & DA6=0

# **5.0 ELECTRICAL PARAMETERS**

#### 5.1 Absolute Maximum Ratings

at: Ta= 0 to 70 °C, VSS=0V

| Name                          | Symbol | Range           | Unit |

|-------------------------------|--------|-----------------|------|

| Maximum Supply Voltage        | VDD    | -0.3 to +6.0    | V    |

| Maximum Input Voltage         | Vin    | -0.3 to VDD+0.3 | V    |

| Maximum Output Voltage        | Vout   | -0.3 to VDD+0.3 | V    |

| Maximum Operating Temperature | Торд   | 0 to +70        | oС   |

| Maximum Storage Temperature   | Tstg   | -25 to +125     | oC   |

#### **5.2 Allowable Operating Conditions**

at: Ta= 0 to 70 <sup>o</sup>C, VSS=0V

| Name              | Symbol | Min.      | Max.       | Unit |

|-------------------|--------|-----------|------------|------|

| Supply Voltage    | VDD    | 4.0       | 6.0        | V    |

| Input "H" Voltage | Vih1   | 0.4 x VDD | VDD +0.3   | V    |

| Input "L" Voltage | Vil1   | -0.3      | 0.15 x VDD | V    |

| Operating Freq.   | Fopg   | -         | 15         | MHz  |

#### 5.3 DC Characteristics

at: Ta=0 to 70 °C, VDD=4.0V ~ 6.0V, VSS=0V

| Name                                                              | Symbol | Condition  | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------------------|--------|------------|------|------|------|------|

| Output "H" Voltage, except open-<br>drain pins: pin #s 16, 17, 29 | Voh1   | loh=-50uA  | 4    |      |      | V    |

| Output "H" Voltage, pin #s 16, 17, 29                             | Voh2   | loh=-1mA   | 4    |      |      | V    |

| Output "L" Voltage                                                | Vol    | Iol=8mA    |      |      | 0.45 | V    |

|                                                                   |        | Active     |      | 18   | 24   | mA   |

| Power Supply Current                                              | ldd    | Idle       |      | 1.3  | 4.0  | mA   |

|                                                                   |        | Power-Down |      | 50   | 80   | uA   |

| RST Pull-Down Resistor                                            | Rrst   | VDD=5V     | 50   |      | 150  | Kohm |

| Pin Capacitance                                                   | Cio    |            |      |      | 15   | pF   |

#### **5.4 AC Characteristics**

at: Ta=0 to 70 °C, VDD=4.0V ~ 6.0V, VSS=0V

| Name                 | Symbol | Condition   | Min.   | Тур. | Max.  | Unit |

|----------------------|--------|-------------|--------|------|-------|------|

| Crystal Frequency    | fXtal  |             |        | 8    |       | MHz  |

| PWM DAC Frequency    | fDA    | fXtal=8MHz  | 31.25  |      | 31.62 | KHz  |

| PWM DAC Frequency    | fDA    | fXtal=12MHz | 46.875 |      | 47.43 | KHz  |

| HS Input Pulse Width | tHIPW  | fXtal=8MHz  | 0.3    |      | 12    | uS   |

| VS Input Pulse Width          | tVIPW | fXtal=8MHz  | 3   |    |   | US |

|-------------------------------|-------|-------------|-----|----|---|----|

| HS Input Pulse Width          | tHIPW | fXtal=12MHz | 0.2 |    | 8 | US |

| VS Input Pulse Width          | tVIPW | fXtal=12MHz | 2   |    |   | US |

| HSYNC to HBLANK Output Jitter | tHHBJ |             |     |    | 5 | NS |

| H+V to VBLANK Output Delay    | tVVBD | fXtal=8MHz  |     | 16 |   | uS |

| H+V to VBLANK Output Delay    | tVVBD | fXtal=12MHz |     | 10 |   | uS |

| VS Pulse Width in H+V Signal  | tVCPW | fXtal=8MHz  | 32  |    |   | uS |

| VS Pulse Width in H+V Signal  | tVCPW | FXtal=12MHz | 20  |    |   | uS |

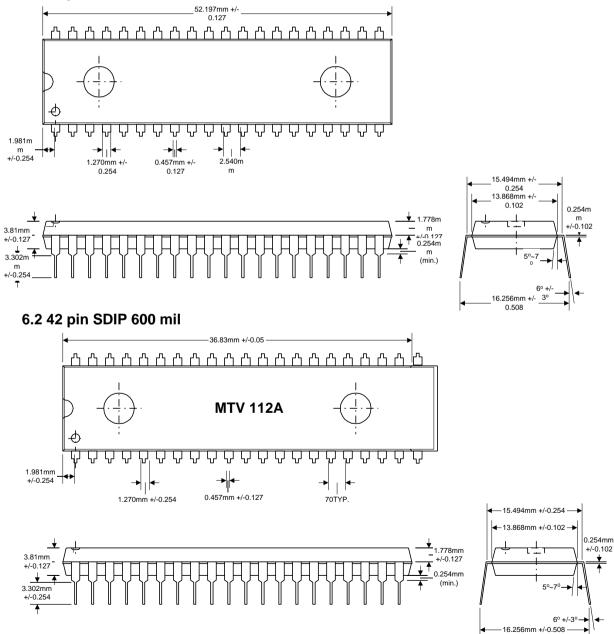

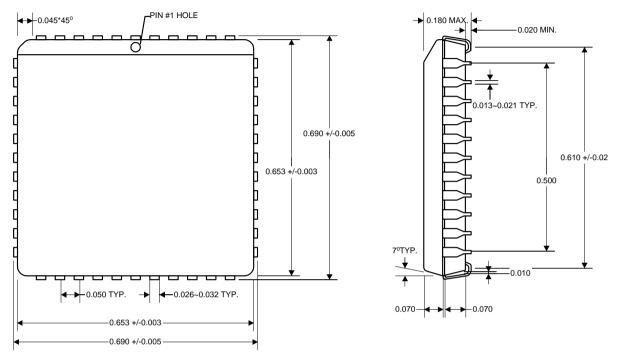

## **6.0 PACKAGE DIMENSION**

## 6.1 40 pin PDIP 600 mil

## 6.3 44 pin PLCC Unit: inch

# 7.0 Ordering Information

Standard configurations:

| Prefix | Part Type | Package Type | Other Information |

|--------|-----------|--------------|-------------------|

|        | 112A      | N: PDIP      |                   |

| MTV    | TIZA      | V: PLCC      |                   |

Part Numbers: